고정 헤더 영역

상세 컨텐츠

본문

728x90

1006

TOOL : Quartus Prime Lite Edition(Ver.18.1)

Board : DE1-SoC

FPGA : ALTERA CycloneV SoC (5CSEMA5F31C6N)

LANGUAGE : Verilog(Ver.2001)

PWM(Pulse Width Modulation)

Duty ratio를 변경하여 펄스 폭을 조절하는 변조 방식이다.

출력 전압값을 기준으로 일정한 Duty동안 High를 유지하고,

나머지는 Low를 내보내 출력 신호를 조절한다.

이때 일정한 주기 안에서 전압이 인가와 끊어짐이 반복되면서 소모 전력이 바뀐다.

PWM을 사용 예로는

모터제어, LED 밝기 제어가 있다.

[my_reg2.v] addr을 2bit로 offset을 2개에서 4개로 늘림

저번시간에 만들어 봤던 MASTER - SLAVE AVALON BUS 모델의

SLAVE 부분을 PWM으로 수정해봤다.

Block_Diagram

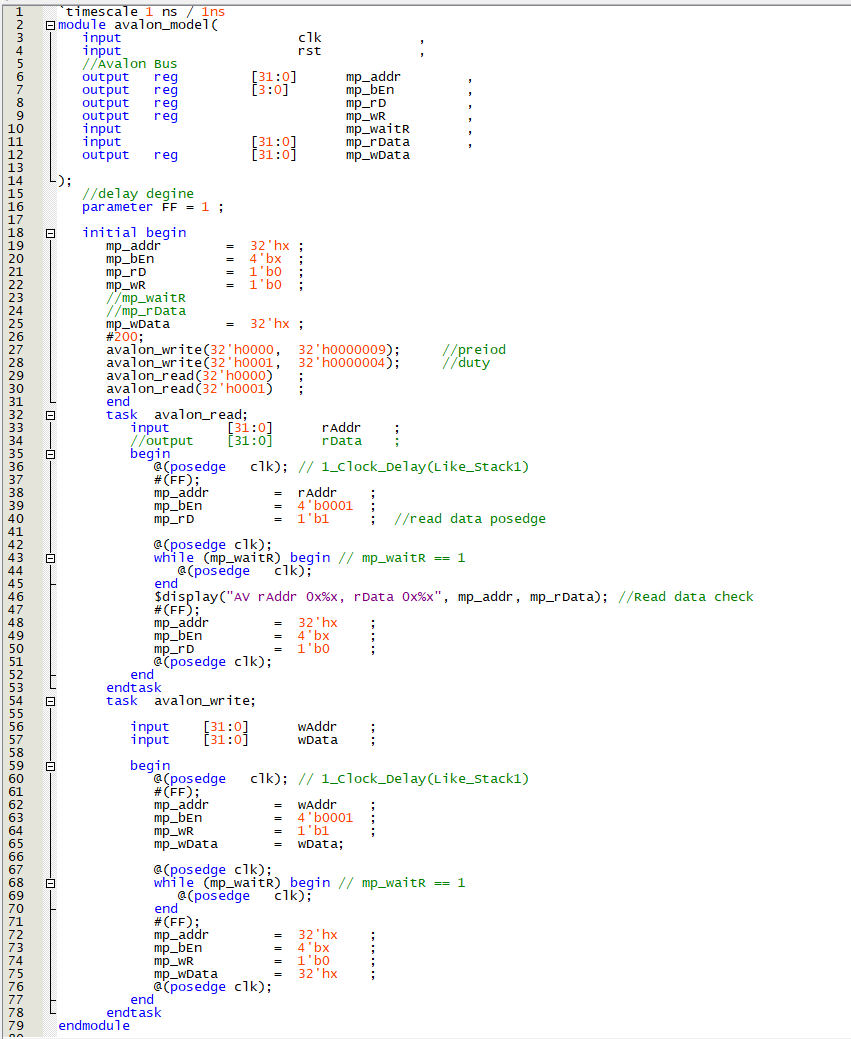

AVALON MODEL CODE

-wirte signal

- Avalon model Tb

Avalon tcl

my_reg

Register Map

SIMULATION 결과

1. WRITE / READ

2. PWM_OUT

728x90

'설계공부 > SoC' 카테고리의 다른 글

| SoC - NiosⅡ(DE1-SoC) - 6 RTL 설계 (0) | 2023.10.11 |

|---|---|

| SoC - NiosⅡ(DE1-SoC) -4 RTL 설계 (0) | 2023.10.05 |

| SoC - NiosⅡ(DE1-SoC) -3 RTL 설계 (0) | 2023.10.04 |

| SoC - NiosⅡ(DE1-SoC) -2 crc / pwm (0) | 2023.09.08 |

| SoC - NiosⅡ(DE1-SoC) -1 (0) | 2023.09.07 |