고정 헤더 영역

상세 컨텐츠

본문

0907

SoC 설계

기본적으로 IP 설계는 BYTE를 사용하게 된다.

왜그럴까? 옛부터 사용하던 구성방식이 고착화되어서 그렇다.

IP설계

상세 Data flow

위 / 다이어 그램과

아래 / 차후 설계 예정 다이어그램

실습 과정

- quartus prim 18.1 lite 버전 사용

- Nios II Command Shell 사용

Board에 sof File DownLoad 후 진행하였다.

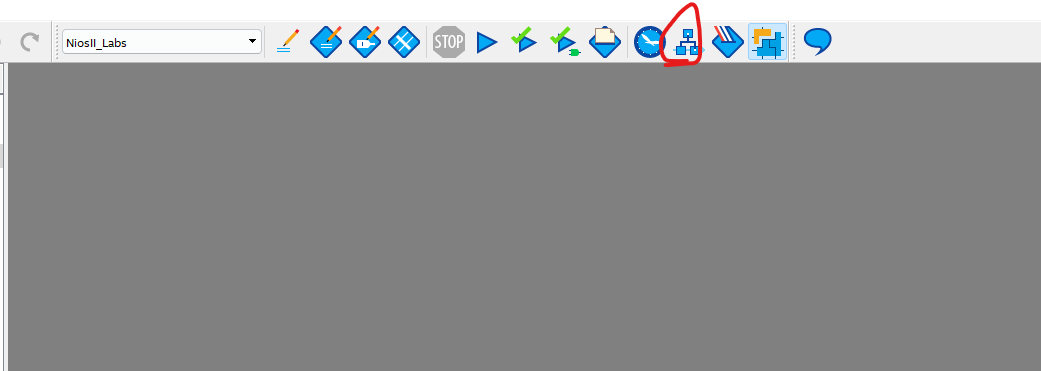

Quartus prim 18.1 lite - programmer

Sof DownLoad 진행

[Nios II Command Shell]

리눅스는 동사+ 명사로 되어 있다.

pwd - 현재 directory

ls - directory list

ls *.@@@@@

~.확장자 >> 타이핑한 확장자들만 확인 할 때 사용

Address 확인

- quartus prim 18.1 lite 버전 사용

- platform Designer(cleck)

0xa2090의 주소값을 확인 하였다.

레지스터에 0xa2090의 주소값을 넣어 동작을 확인했다.

입력 후, 보드 동작 확인 후

Nios II Command Shell결과

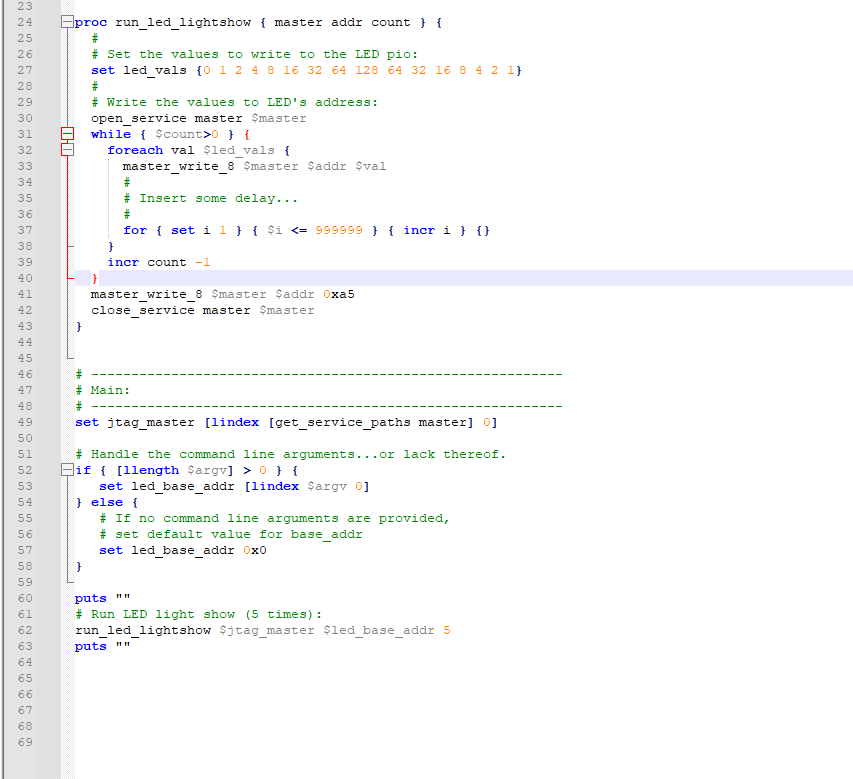

proc를 통해 함수에 run_led_lightshow 변수를 넣고,

다음 변수인 master address count 값은 함수에 지정해 주었다.

LED TCL 파일 열어서 레지스터 제어

LED 속도를 더 빠르게하여 실행을 더 빠르게 할 수 있도록 했다.

>> i의 딜레이 값 1Bit 삭제,

adder 값 0xa5로 변경

Tx보낼때 이렇게 제어를 하면 된다.

led.tcl 파일 복사

Code 해석

첫 번째 줄 >> jtag_master라는 변수에다 마스터를 치환

두 번째 줄 >> jtag_master라는 마스터를 오픈

세 번째 줄 >> jtag_master라는 마스터와 0xa2090 주소에다 0xf0라는 데이터를 입력

네 번째 줄 >> jtag_master라는 마스터를 close

// open 후 꼭 close를 해줘야 한다. 그렇지 않으면 무한 루프

다섯 번째 줄 >> "test done!"을 출력.

Tcl 파일 변경한 후

Nios II Command Shell를 통해 Board 동작 테스트 진행

Board 동작 결과

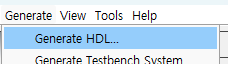

QSYS

시뮬레이션 돌릴 수 있는 환경을 만들 수 있다.

생성된 .html 실행 결과

블록 다이어 그램의 정보를 확인 가능하다.

'설계공부 > SoC' 카테고리의 다른 글

| SoC - NiosⅡ(DE1-SoC) - 6 RTL 설계 (0) | 2023.10.11 |

|---|---|

| SoC - NiosⅡ(DE1-SoC) - 5 PWM 설계 (0) | 2023.10.06 |

| SoC - NiosⅡ(DE1-SoC) -4 RTL 설계 (0) | 2023.10.05 |

| SoC - NiosⅡ(DE1-SoC) -3 RTL 설계 (0) | 2023.10.04 |

| SoC - NiosⅡ(DE1-SoC) -2 crc / pwm (0) | 2023.09.08 |