고정 헤더 영역

상세 컨텐츠

본문

1005

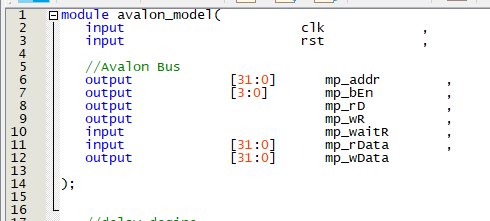

Avalon_bus를 설계해 보았다

Avlon_bus_Data_sheet

초기의 cpu형태

reg 선언 안해줘서 나오는 오류가 난다.

따라서 reg를 붙여줘 오류를 해결

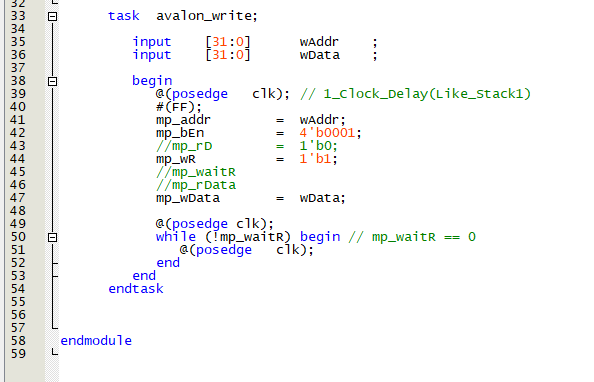

추가적으로 Delay가 존재하기에 Delay 설계를 했다.

DATA_SHEET를 보면 UKNOUN 값도 있기 때문에 검은색 부분은 X로 둠

버스 모델링은 task다.

Begin은 body부분

procedural 구문처럼 데이터를 받으면 된다.

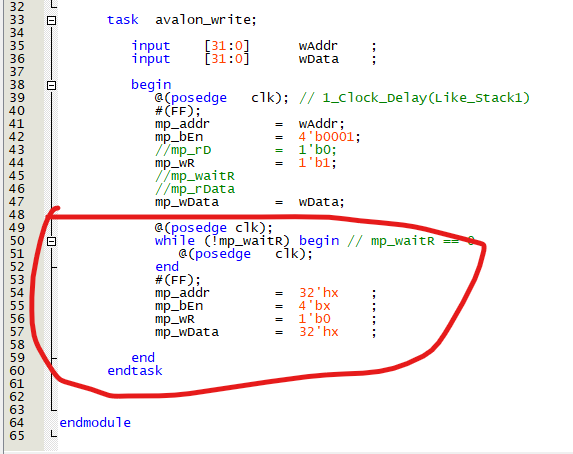

추가적으로

해당 부분 설계

해당부분을 설계완료하여,

전체적인 task를 완성했다.

Test_bench

패턴을 만들어야 하기 때문에 reg

Output은 wire연결

clk을 추가해줬다.

Tcl_file

Modelsim_Simulation 용도의 파일

Vlog를 통해 comfile하기

보고싶은 신호들 추가

SIMULATION결과

DATA_SHEET와 비교

설계한 BUS에 Data 넣어보고 확인

1000번지 Address에 data 넣고 확인(write_Data)

Simulation 결과

Data read write를 할 수 있는 것을 확인했다.

* ? *

게이트 Delay를 통한 Logic Simulation 확인하는 이유?

Timing simulation을 하려면 다 뒤집어 엎어야 하기에

Logic simulation에서 확인

Read data 넣고 확인

Read 값을 확인하기 위해

또 다른 task를 만들었다.

이번에는 read_data용 데이터 값을 넣어줬다.

TEST_BENCH

데이터를 넣은 결과

Simulation과 같이 read_data값이 나오는 것을 확인했다.

Simulation 결과

Task 로 바꿔주기

따로 따로계속 넣어주는걸 방지하기위해 Task로 묶어 한다.

Simulation 결과

clk구문_Task로 바꾸기

여기서 중요한 점은

Initial 구문을 forever로 바꿔줘야 하는것이다.

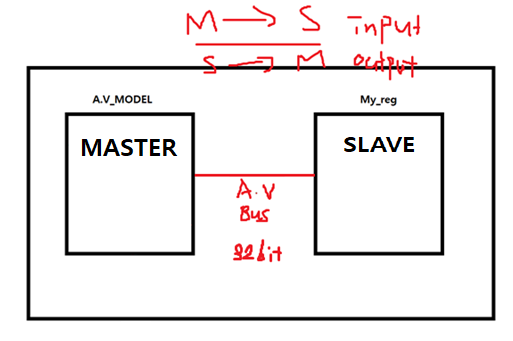

My_reg 모듈 만들기

A.V_model의 값의 출력을 받아 동작하는 My_reg 모듈을 만들었다.

assign 구문에서 왼쪽은 꼭 wire 값이 와야함

Test_bench

Simulation결과

200초 이후

(w_Data : AABBCCDD) > Negedge(DEADBEEF)

read address : 32bit 0x1000 > read address : 32bit 0x2000

Bus설계 후 직접 boad 동작해보기

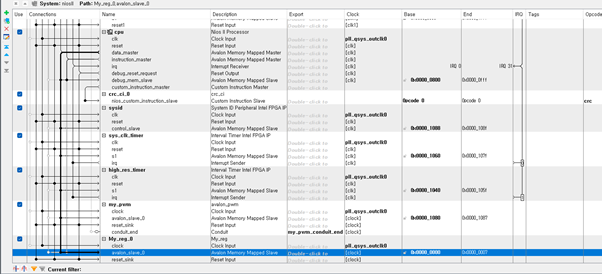

Platform_Designer

Componet생성

File 추가

Slave 설정과 Slave_Type설정

Interface설정

설계 이후 Bus형태

Connect(Master/Slave 연결 후 저장)

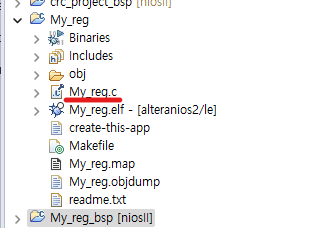

Nios2_BSP_Eclips

파일 없기 때문에 simple.c 파일을 복사 붙여넣어 파일생성,

이후 드래그를 통해 파일 등록

My_reg_bsp_설정

My_reg.c (Memory Access)

포인터를 통해 주소에 접근해 123값을 넣고 읽은 결과

보드

'설계공부 > SoC' 카테고리의 다른 글

| SoC - NiosⅡ(DE1-SoC) - 6 RTL 설계 (0) | 2023.10.11 |

|---|---|

| SoC - NiosⅡ(DE1-SoC) - 5 PWM 설계 (0) | 2023.10.06 |

| SoC - NiosⅡ(DE1-SoC) -3 RTL 설계 (0) | 2023.10.04 |

| SoC - NiosⅡ(DE1-SoC) -2 crc / pwm (0) | 2023.09.08 |

| SoC - NiosⅡ(DE1-SoC) -1 (0) | 2023.09.07 |