고정 헤더 영역

상세 컨텐츠

본문

[23.07.31 ~ 23.08.04 (5일)]

0802~0804

TOOL : XILINX - VIVADO

사용 FPGA : Artix-7 사의 (XC7A35T-1CPG236C)

사용 BOARD - Basis 3

논리 게이트와 회로 구성 요소를 통해 데이터가 전당 되는 경로인

Critical path는 전체 회로의 지연시간이 가장 큰 부분을 차지한다.

이 곳에서 어떻게 하느냐가 동작속도를 결정하며, 데이터가 정확한 타이밍에 입/출력 될 수 있도록 하는 것이 중요하다.

Critical path에서는 Glitch와 propagation delay가 발생한다.

이를 어떻게 최적화 하는지가 중요한 것이다.

안정성을 높이기 위해서는 Feedback system을 갖는 회로를 사용한다.

Feedback system 에는 LATCH / FLIP FLOP가 있지만 FLIP FLOP을 주로 사용한다.

LATCH와 다르게 FLIP FLOP은 지속적으로 값을 할당하지 않고 1CLK을 보장해

입력을 CAPUTURE 하여 출력하기에 CONTROL이 가능하다.

LATCH는 SR LATCH와 D LATCH가 있다.

SR LATCH는 동시에 입력이 들어왔을 때

SIMULATION 상에서 UNKNOUN값 또는 오류가 난다. \

또한 지속적으로 값을 할당하면서 출력하기 때문에 불안정하다.

따라서 쓰지않는다

D LATCH는 SR LATCH에 NOT게이트가 붙어있는 형태이다.

동시에 들어왔을때도 값을 반전시켜 오류가 나지않고, 지속적으로 값을 받을 수 있다,

하지만 계속해서 값이 들어오기 때문에 Control하기 어려운데 이를 해결하기 위해 FLIP FLOP을 사용한다.

FLIP FLOP을 통해 값이 1CLK을 보장하여 값을 받아 안정적으로 값을 할당 받을 수 있기 때문이다.

입력 직 후 바로 받지 않고 1CLK 늦게 받기 때문에 입력의 GLITCH를 피할 수 있다.

RISING_EDGE마다 값이 변화한다.

FLIP_FLOP의 경우 입력을 CAPTURE하여 값을 출력하기 때문에

SETUP TIME과 HOLD TIME이 존재하는데 이것을 맞춰주지 않는다면 값이 제대로 나오지 않는다.

따라서 유의하며 CLK을 설정해줘야한다.

또한 시스템의 안정성을 위해

Synchronous 시스템으로 설계한다.

ASynchronous 보다 CLK을 기반으로 동작하기에 타이밍 문제도 감소하기 때문이다.

따라서 안정적으로 하기 위해 HOLD/SETUP TIME을 기준으로 CLK의 주기를 결정한다.

이를 7SEG의 LED가 지속적으로 ON-OFF를 반복하게 만들어, 제대로 동작하는지 알아보았다.

그러기 위해선 CLK_DIVIDER(CLK을 나눠주는역할)

COUNTER(연산/ RESET용) DECODER가필요하다.

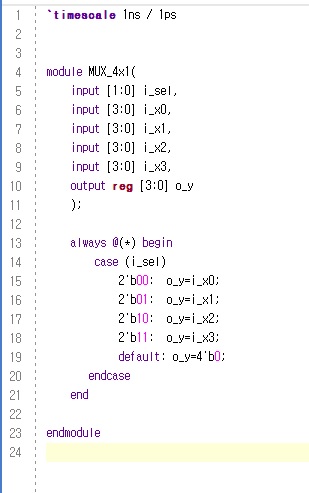

4x1 MUX

[1:0] i_sel = 0 이면 일의 자리수 출력

i_sel = 1 이면 십의 자리수 출력

i_sel = 2 이면 백의 자리수 출력

i_sel = 3 이면 천의 자리수 출력

2BIT_ COUNTER

DECODER

BCD_TO_FND_DECODER

Digit_Splitter

값을 1/10/100/1000자리로 나눠 할당받기 위한 모듈

최종 모듈

8BIT계산기 완성

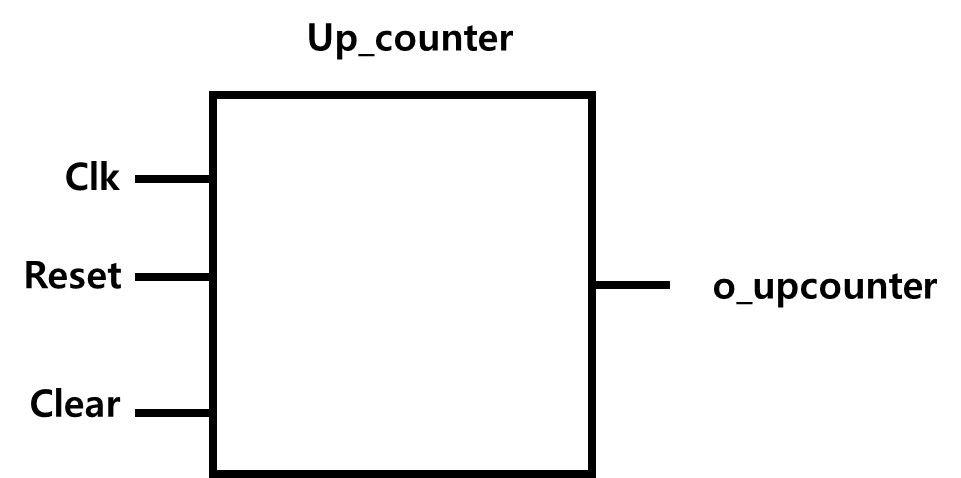

Up_Counter_1구현

clock_divider

clock divider 즉 분주기를 만들기 위해서는 다음과 같은 논리가 필요하다.

reset 스위치를 담당하는 변수 명을 'reset'으로 한다.

clear 스위치를 담당하는 변수 명을 'i_clear'으로 한다.

run (스위치가 꺼질때는 stop) 스위치를 담당하는 변수 명을 i_enable으로 한다.

동작의 형태

reset == 1일 때 (reset_on) => r_counter = 0(분주기의 counter 초기화)

clear == 1일 때 (clear_on) => r_counter = 0(분주기의 counter 초기화)

enable == 1일 때 (run_on) => r_counter = r_counter + 1(분주기 counter + 1)

enable == 0일 때 ( run _off) => r_counter = 0(분주기 counter 초기화)

reset / i_clear이 1이 될 때,

분주기의 카운터는 0, 그렇지 않으면 i_enable 1이 되며,

이 경우 두 가지 상황으로 나뉘어 진다.

r_counter 가 '10000000 - 1'이 되는 경우 o_clk이 1이 되고 r_counter은 0이 된다.

그렇지 않으면 r_counter는 1씩 증가한다.

r_counter가 '10000000-1'될때

o_clk의 peak가 나온다.

r_counter가 '10000000-1'될때 o_clk이라는 peak가 나오게 하는 코드를 만들었다.

이럴경우 너무 빨라 사람 눈으로 감지하기 어렵다.

따라서 알맞게 CLK을 나눠줄 수 있는 CLOCK_DIVIDER를 통해 CLK을 조절한다.

Input은 clk, reset, clear

Output은 14bit o_upcounter다.

upcounter 동작설명

reset 1일때, upcounter는 0이 된다.

clear(SW on)1이 될때, upcounter는 1의 값이 할당 된다.

반대로 clear(SW off)이고 reset 0일때, upcounter는 계속 Counting된다.

CODE해석

LED 4개의 동작을 해야하기 때문에,

o_upcounter를 9999까지 지정, reset 과 i_clear가 둘 중 하나가 1이 될 때, o_upcounter는 0이 된다.

그렇지 않고, o_upcounter가 9999가 되면, o_upcounter은 0으로 초기화 된다.

9999가 아닐 경우, o_upcounter은 계속해서 1을 더한다.

(1). reset 1일 때, 카운터가 늘어나지 않는다.

(2). run_stop 1일 때, o_clk(w_clk)1일 때마다 카운터가 증가하는 것을 알 수 있다.

(3). run_stop 0이거, i_clear(clear switch on) 1일 때 카운터가 중단된다.

Calculator

SW 1,10 ON

결과 3

FSM_LED

(Moore Machine) FSM 연습용

Moor machine / Mealy machine가 있지만

안정성이 높고 설계하기 쉬운 Moor machine로 설계했다.

Stopwatch

FSM_stopwatch

PushButtonOneShot

block_diagram

RTL_VIEW

최종

Calculator

완성,

'설계공부 > VIVADO' 카테고리의 다른 글

| Verilog HDL - LED_FSM(Moore / Mearly) (0) | 2023.12.21 |

|---|---|

| Verilog HDL - VIVADO_2(7segment / decoder) (0) | 2023.09.18 |

| Verilog HDL - VIVADO_1(FULLADDER_4BIT / 8BIT) (0) | 2023.09.17 |