고정 헤더 영역

상세 컨텐츠

본문

[23.07.31 ~ 23.08.04 (5일)]

0731

TOOL : XILINX - VIVADO

사용 FPGA : Artix-7 사의 (XC7A35T-1CPG236C)

사용 BOARD - Basis 3

반도체 설계 절차

Verilog 용어

Behavior Modeling - I/O(입출력) 반응에 의해 묘사되는 요소 - 오직 회로의 기능만

모듈이 어떻게 동작하는지를 기능위주로 설명하는 모델

Structural Modeling - 서로 연결하는 lower-level의 요소들로 묘사되는 요소로

Gate level이며 주로 상위의 설계물을 설계할 때 사용된다.

RTL(Register Transfer Level) – 설계 합성

Synthesis(합성)

HALF_ADDER

carry값과 sum값을 저장할 수 있는 변수를 선언하고

i_a와 i_b를 and / or하여 그 변수에 값이 저장되도록 구현

FULL_ADDER

FULL_ADDER를 구현 하기 위해 HALF_ADDER 2개를 사용하여 구현하였다.

HALF_ADDER 를 Instantaition하여 사용하였다.

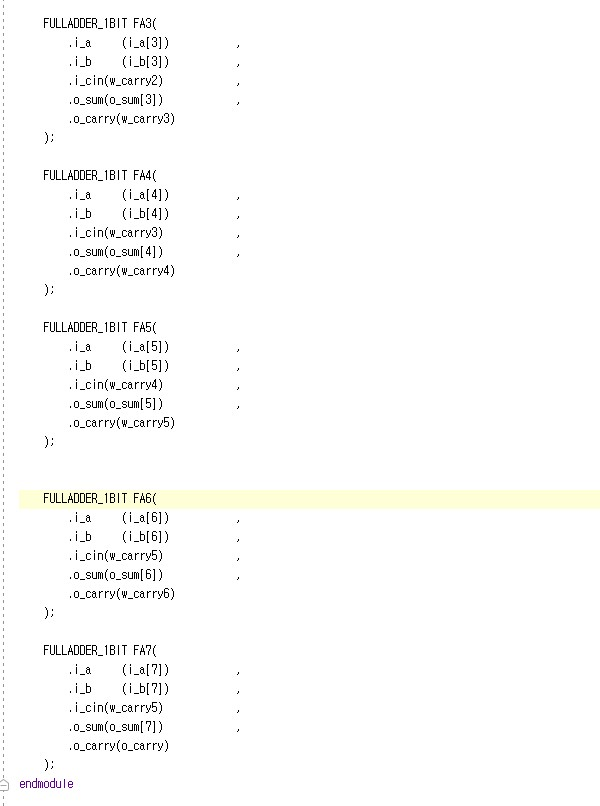

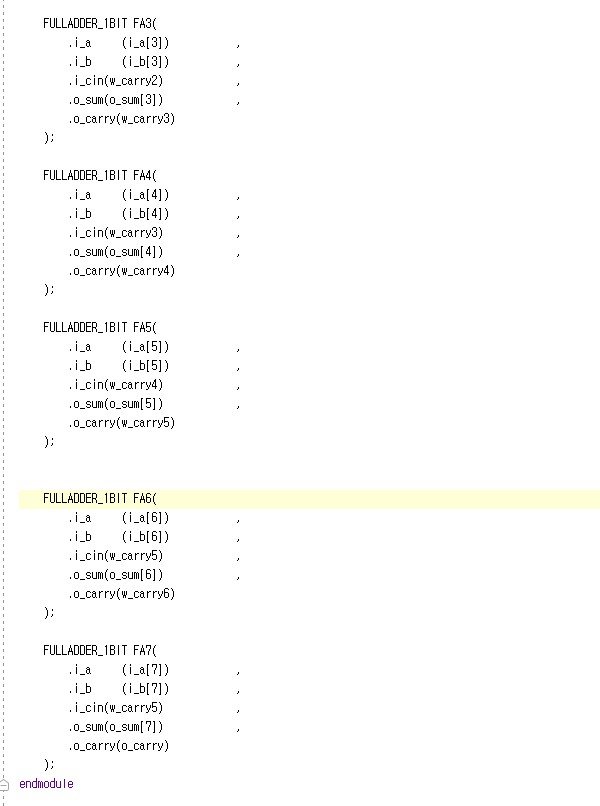

FULL_ADDER_4BIT

FULL_ADDER_8BIT를 구현하기 위해 FULL_ADDER_4BIT를 만들었다.

FULL_ADDER_8BIT

만들어 놓은 FULL_ADDER_4BIT을 Instantaition하여, 8BIT_ADDER를 만들었다.

TEST_BENCH_CODE

TEST_BENCH_SIMULATION

i_a와 i_b를 더한 결과가 o_sum에 나오도록 구현,

o_carry는 o_sum이 8비트 이상을 할당 받았을 때 발생된다.

TEST_BENCH_INPUT_SWITCH

BOARD동작 결과

t3(i_b1 ) / w16(i_a2 ) SW가 켜지면 3이 출력

즉 LED2번이 켜지는 것을 볼 수 있다.[0번 부터 시작 따라서 3]

따라서 제대로 작동 하는것을 알 수 있었다.

'설계공부 > VIVADO' 카테고리의 다른 글

| Verilog HDL - LED_FSM(Moore / Mearly) (0) | 2023.12.21 |

|---|---|

| Verilog HDL - VIVADO_3~5(7segment~TIMER) (0) | 2023.12.14 |

| Verilog HDL - VIVADO_2(7segment / decoder) (0) | 2023.09.18 |