고정 헤더 영역

상세 컨텐츠

본문

HDL: Verilog(2001)

Synthesis: Intel(Altera)_Quartus prime 18.1

Simulation: Intel(Altera)_ModelSim 10.5b

Board: Intel(Altera)_DE1_SoC (FPGA와 HPS가 결합된 SoC)

FPGA(device): Intel(Altera)_Cyclone V(5CSEMA5F31c6)

HPS(Hard Processor System): ARM_Coretex-A9

8x8mult을 만들기 위한 module 구현 중.

uart / mult 8*8에 사용할 shifter를 만들기 위한 연습과정

shifter_blockdiagram

Code

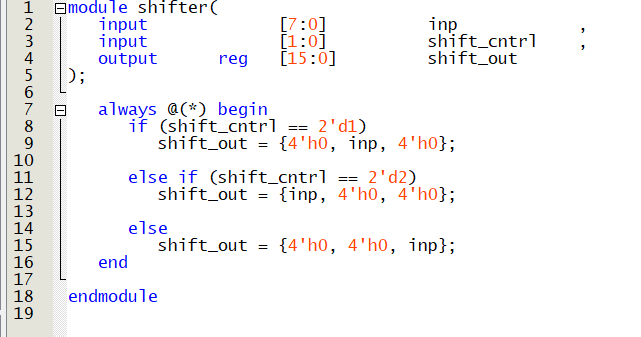

shifter.v

input, output 값 입력 후,

cntrl값을 조건 매개체로 사용, 0이나 3일때 no shift

1일때 왼쪽으로 shift 한 뒤, 나머지 값 0

2일때 왼쪽으로 한번 더 shift 한 뒤, 나머지 값 0

이 나올 수 있도록 조건을 줬다.

2나 0 or 3 조건 사용시 4'h0 두개를 8'h0로 바꾸어 사용가능

tb_shifter.v

initial begin-end 구문을 사용하여 inp, shift_cntrl 초기 값을 설정 한 뒤,

조건을 제어할 수 있도록 20ns 마다 cntrl 값을 +1씩 증가 되도록 설계 했다.

simulation 결과

shiftt_cntrl이 0 or 3 일때 no shift /

1일때 왼쪽 으로 shift 한 뒤 나머지 0으로 맞춰줌

2일때 왼쪽 으로 shift 한번 더 한뒤 나머지 0 그 결과가 제대로 동작함을 검증했다.

'설계공부 > Verilog' 카테고리의 다른 글

| verilog - reg16(bit_clear내용) (0) | 2024.05.11 |

|---|---|

| verilog - 7segment (0) | 2024.05.07 |

| verilog-mux4 (0) | 2024.05.06 |

| verilog-mult4x4 (0) | 2024.05.06 |

| verliog-adder (0) | 2024.05.06 |