고정 헤더 영역

상세 컨텐츠

본문 제목

FULL CHIP CUSTOM ONE CHIP DESIGN - 6(4X1 MUX LOGIC / SWITCH)

본문

4X1MUX

복수회로에서 입력되는 4개의 신호 중 어느 하나의 입력신호를 선택하여 출력회로에 내보내주는 논리 회로이다.

4X1MUX 진리표

구현방법

4X1MUX LOGIC GATE

(Inverter 2EA)*2 + (3Nand 4EA)*6 + (4Nand 1EA)*8=36개 의 Tr로 구성하여 제작했다.

<4X1MUX LOGIC_SCHEMATIC>

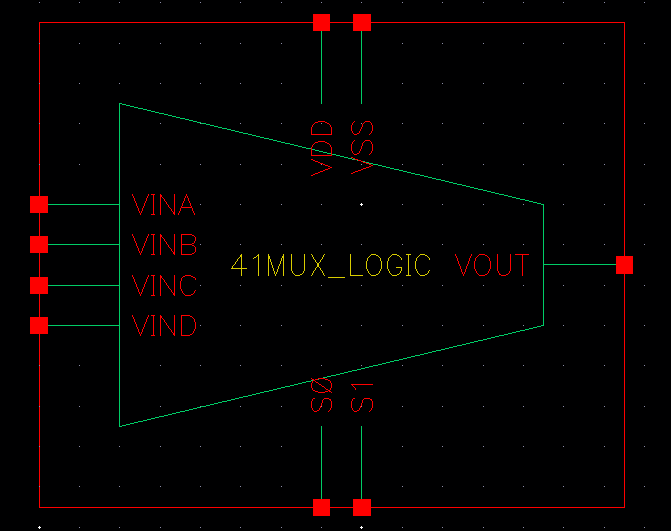

<4X1MUX LOGIC_SIMBOL>

<4X1MUX LOGIC_TEST_SCHEMATIC>

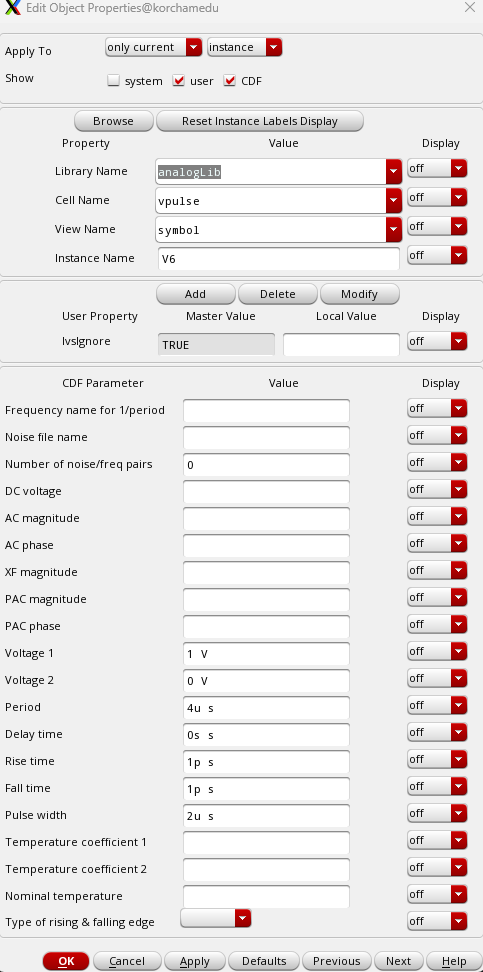

<SETTING>

C / D

S0 / S1

S0와 S1은 Pulse로 두어 지속적인 신호를 보내도록 했다 그에 따른 SIMULATION을 관찰하였다.

<4X1MUX LOGIC_SIMULATION_WAVE FORM>

<4X1MUX LOGIC_STICK DIAGRAM>

<4X1MUX LOGIC_LAYOUT>

세로 : 7.4um

가로 : nMOS 13.63um

AREA : 100.862um2

구현방법

4X1MUX CMOS SWITCH

(CMOS 2EA)*6 + (Inverter 2EA)*2 = 16개 의 Tr로 구성하여 제작했다.

<4X1MUX SWITCH_SCHEMATIC>

<4X1MUX SWITCH_SIMBOL>

<4X1MUX SWITCH_TEST_SCHEMATIC>

<4X1MUX SWITCH_LAYOUT>

세로 : 8.075 [um]

가로 : nMOS 6.02 [um]

AREA : 48.6115 [um2]

2X1 MUX와 마찬가지로 4X1 MUX 또한 GATE LOGIC보다 SW로 설계하는 것이 Tr의 갯수를 줄일 수 있었고,

LAYOUT 설계 시 크기 또한 줄어드는것을 확인했다.

'설계공부 > Full Custom IC One Chip Design' 카테고리의 다른 글

| FULL CHIP CUSTOM ONE CHIP DESIGN - 8(16X1 MUX LOGIC / SWITCH) (0) | 2023.08.19 |

|---|---|

| FULL CHIP CUSTOM ONE CHIP DESIGN - 7(8X1 MUX LOGIC / SWITCH) (0) | 2023.08.19 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 5(2X1 MUX LOGIC / SWITCH) (0) | 2023.08.07 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 5(3-4 NAND, NOR //LAYOUT) (0) | 2023.08.07 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 4(2NAND, 2NOR //LAYOUT) (0) | 2023.08.07 |