고정 헤더 영역

상세 컨텐츠

본문 제목

FULL CHIP CUSTOM ONE CHIP DESIGN - 3(INVERTER, 2NAND, 2NOR, WIDTH)

본문

INVERTER

VIRTUOSO TOOL을 사용하여 pMOS가 ON되는 길이와 nMOS가 ON되는 길이가 1:1이 되도록 하는 pMOS의 W(WIDTH)값을 구해보겠다. W값을 구하는 이유는 pMOS의 Q POINT를 알아내기 위하여 구하는 과정이다.

nMOS의 W값은 1um로 가정하고

pMOS의 W값을 변수로 주어 적절한 W값을 구하는 방식을 사용했다.

- 다른 GATE 들도 대부분 동일하게 진행

<NOT_SECHEMATIC>

TEST를 하기 위해 더미를 만들어 SIMULATION을 돌린다.

그렇기 때문에 SIMBOL과 TEST_SCHEMATIC을 추가 제작하였다.

<NOT_SIMBOL>

<NOT_TEST_SCHEMATIC>

추가 제작 후 SIMULATION을 진행하였다.

얻고자하는 WIDTH의 값은 VOUT 출력파형이 (0.5,0.5)지점(500m)을 지나는 그래프를 찾아.

확대해서 WIDTH 범위를 특정하고 소수 둘째자리까지 구해준다.

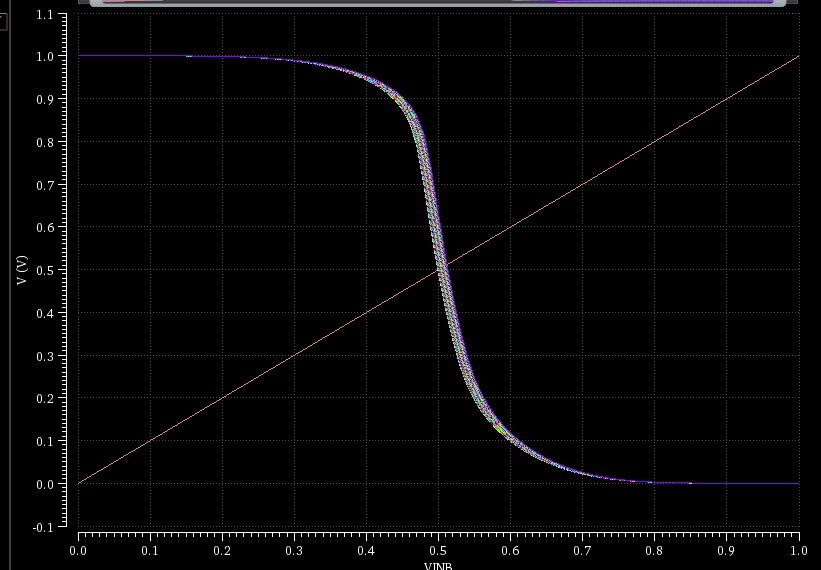

<INVERTER_SIMULATION>

SIMULATION은 Analysis - choosing analysies를 통해 VINB의 값을 조정

tools - parametric Analsis를 통해 진행 범위와 STEP SIZE를 점차 좁혀가며 정확한 W값을 구하게 되었다.

SIMULATION 결과

pMOS의 적절한 W 값은 2.91[um]라는 것을 확인 할 수 있다.

2NAND

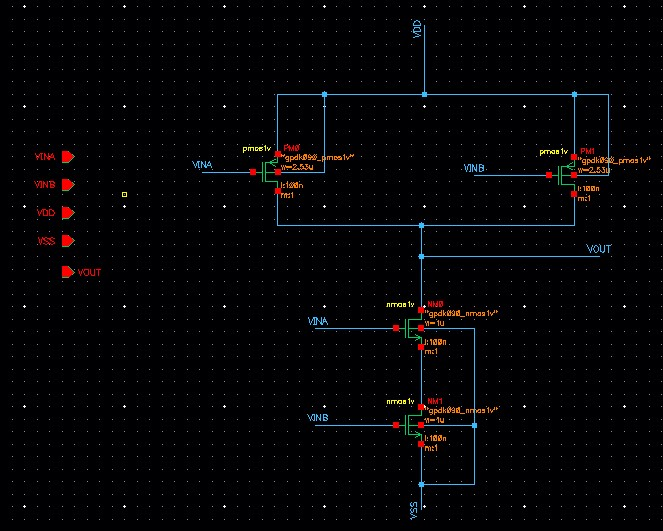

INVERTER와 동일하게 2NAND도 SCHEMATIC을 그린 후 SIMBOL 제작, TEST LIBRARY를 생성하여

SIMULATION을 진행하여 W값을 구하는 방식으로 진행하였다.

<2NAND_SCHEMATIC>

<2NAND_SIMBOL>

<2NAND_TEST_SCHEMATIC>

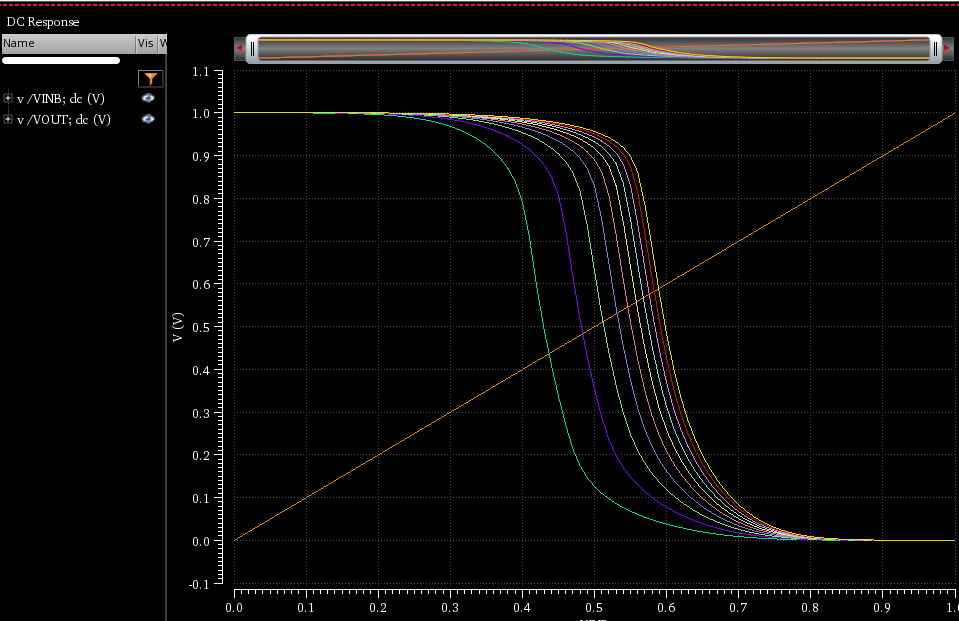

<2NAND_SIMULATION>

첫 번째 SIMULATION의 범위는 1[um]에서 10[um]까지 1[um]씩 증가하며

확인하는 SIMULATION으로 값을 조정하여 확인하였다.

첫 번째 SIMULATION 결과 2[um]와 3[um]사이에 500m값을 나타내는 것을 확인 할 수 있다.

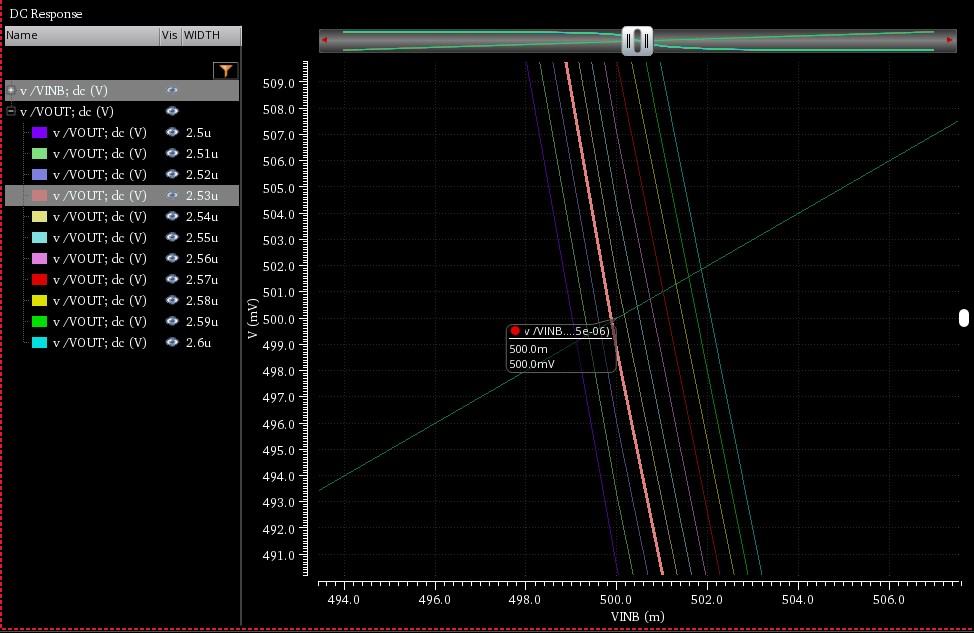

따라서 SIMULATION 할 범위를 2.5[um]와 2.6[um]사이로 줄였으며

그 결과 적절한 W값인 2.53[um]값을 찾을 수 있었다.

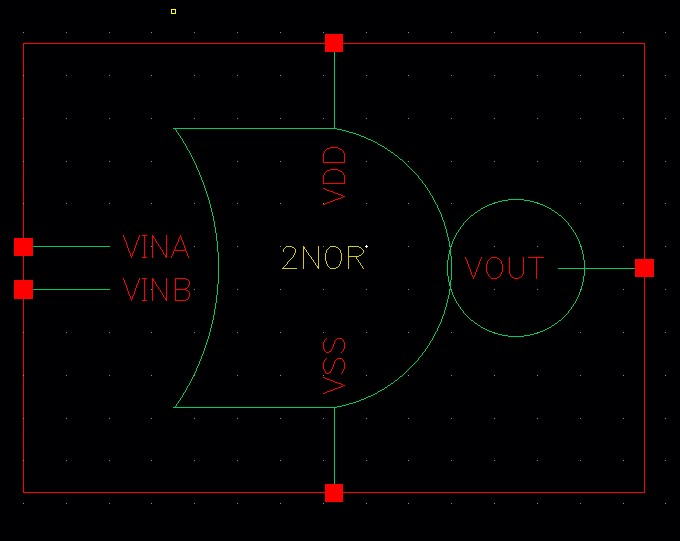

2NOR SCHEMATIC, WIDTH

<2NOR_SCHEMATIC>

<2NOR_SIMBOL>

<2NOR_TEST_SCHEMATIC>

W값은 3.99[um]이 나오게 되어 적용하게 됐다.

'설계공부 > Full Custom IC One Chip Design' 카테고리의 다른 글

| FULL CHIP CUSTOM ONE CHIP DESIGN - 5(2X1 MUX LOGIC / SWITCH) (0) | 2023.08.07 |

|---|---|

| FULL CHIP CUSTOM ONE CHIP DESIGN - 5(3-4 NAND, NOR //LAYOUT) (0) | 2023.08.07 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 4(2NAND, 2NOR //LAYOUT) (0) | 2023.08.07 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 2(SCHEMATIC , STICK DIAGRAM) (0) | 2023.07.25 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 1 (1) | 2023.07.10 |