고정 헤더 영역

상세 컨텐츠

본문

드디어 7월4일이 되어 첫 교육을 받으러 가게 되었다.

9~11시까지 ot진행 후 수업을 하게 되었다.

수업의 내용은 CMOS설계에 대해 배우게 되었다.

CMOS설계 시 CMOS가 무엇인지, Transister를 통해 논리 게이트를 어떻게 만드는지, Transister LayOut을 어떻게 할 것인지를 알고 있어야 하기에 이론적인 내용부터 배우게 되었다.

<이론>

IC(Intraduction circuit)는 하나의 칩에 다 집어넣은 형태로 장점으로는 속도 / 가격 / 저전력이 있다.

대량생산 가능하고 빠르고 POWER 공급전압이 낮기 때문이다.

종류는 크기별로 SoC / ULSI / VLSI / LSI / MSI / SSI 가 있으며,

VLSI 내에 CMOS가 있다.

CMOS(Complementary Metal Oxide Semiconductor)는 상부형 Tr을 갖는 반도체이다.

(NMOS의 성질과 PMOS의 성질이 서로 반대를 이루며, 크기와, 에너지가 동등하게 사용이 되는 Tr)

*상부형 : 서로 반대의 성질을 갖는

CMOS에는 NMOS와 PMOS가 있고, 설계시 CMOS가 무엇인지, Tr을 통해 논리 게이트를 어떻게 만드는지, Tr Layout을 어떻게 작성 할 것인지 인지해야 설계 오류 없이 제대로 설계 할 수 있다.

<물질의 결합 형태>

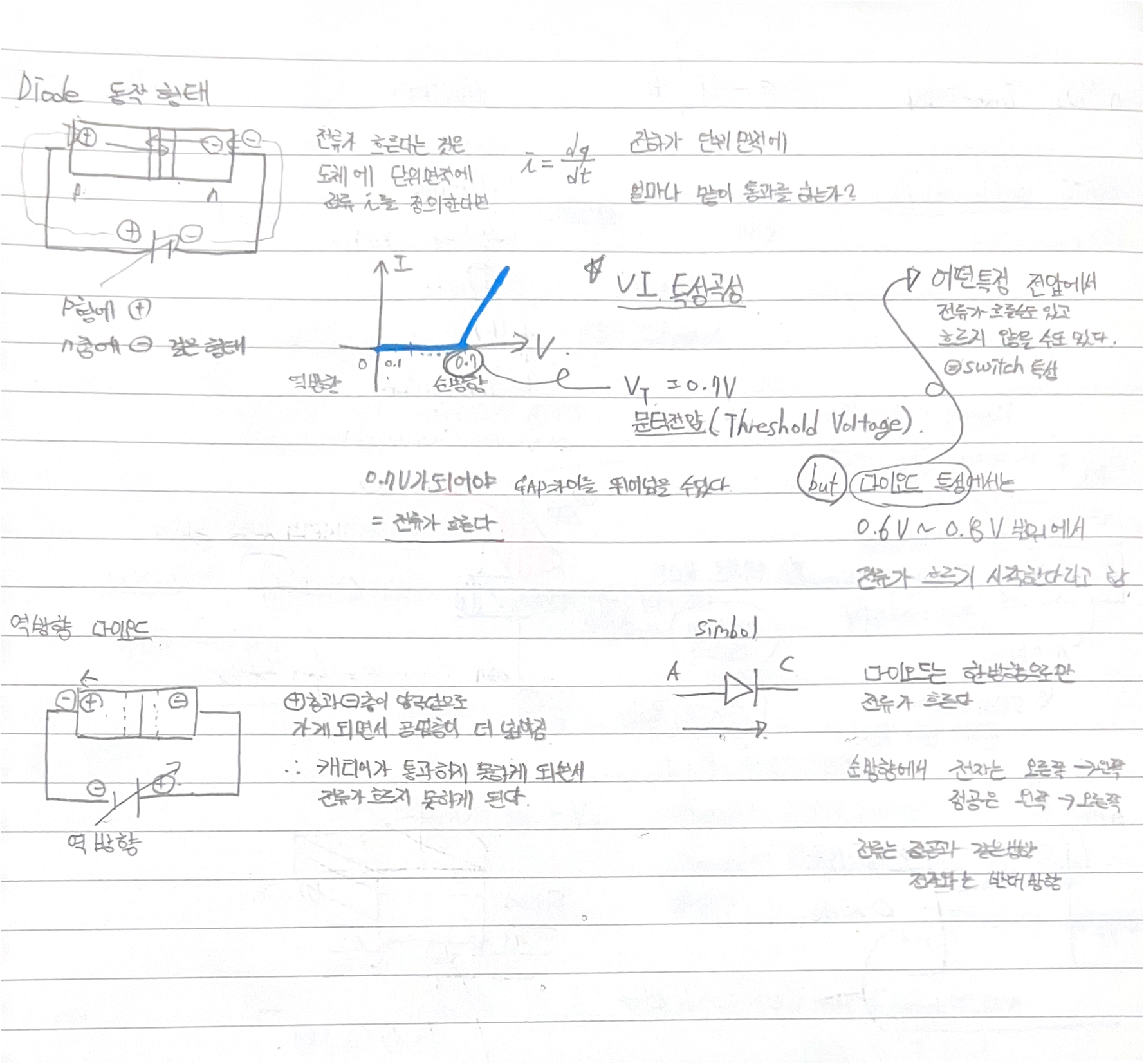

<DIODE 동작형태>

<MOSFET>

MOSFET-(Metal Oxide Semiconductor / Field Effect Transister)

Materials 동작

디지털 논리회로에서 NOR게이트와 NAND게이트 중에서 NAND게이트로 설계하는것이 더 유리하다. 만약 출력이 NAND로 되어있지않다면 이중부정을 통하여 NAND구조로 설계하는것이 좋다.

설계 순서는

1.Schematic

2.Simulation

3.Layout 순으로 작성되며,

각 부분이 만들어 지기위해 선행되어야 하는 부분이 있다.

Schematic을 작성하기 위해서는 진리표, 카르노 맵을 통한 최소화된 함수 값 작성을 줄 알아야 한다.

진리표는 함수값을 표현하기 위해서이다.

또한 Schematic의 작성시 조건이 있다.

1.Tr을 한번씩만 모두 경유 하는 Path를 찾는다.

2.해당 Path가 PMOS NMOS둘다 만족해야한다.

이 두가지 조건을 만족해야 정확한 Schematic을 작성하게 되며, 정확한 Layout을 작성할 수 있다.

Simulation 은 Schematic을 토대로 Simbol을 작성 후 파형을 확인하며 적절한 W(Width)값을 찾아 입력하여 적절한 전압값을 갖는 레이어를 만들게 된다

Layout은 Schematic과 Stick 다이어그램을 토대로 작성하게 되는데, DRC(Design rule chec) 검증과 LVS(Layout Versus Schematic)검증을 해당 과정에서 진행하게 된다.

EX) 2NAND_SCHEMATIC

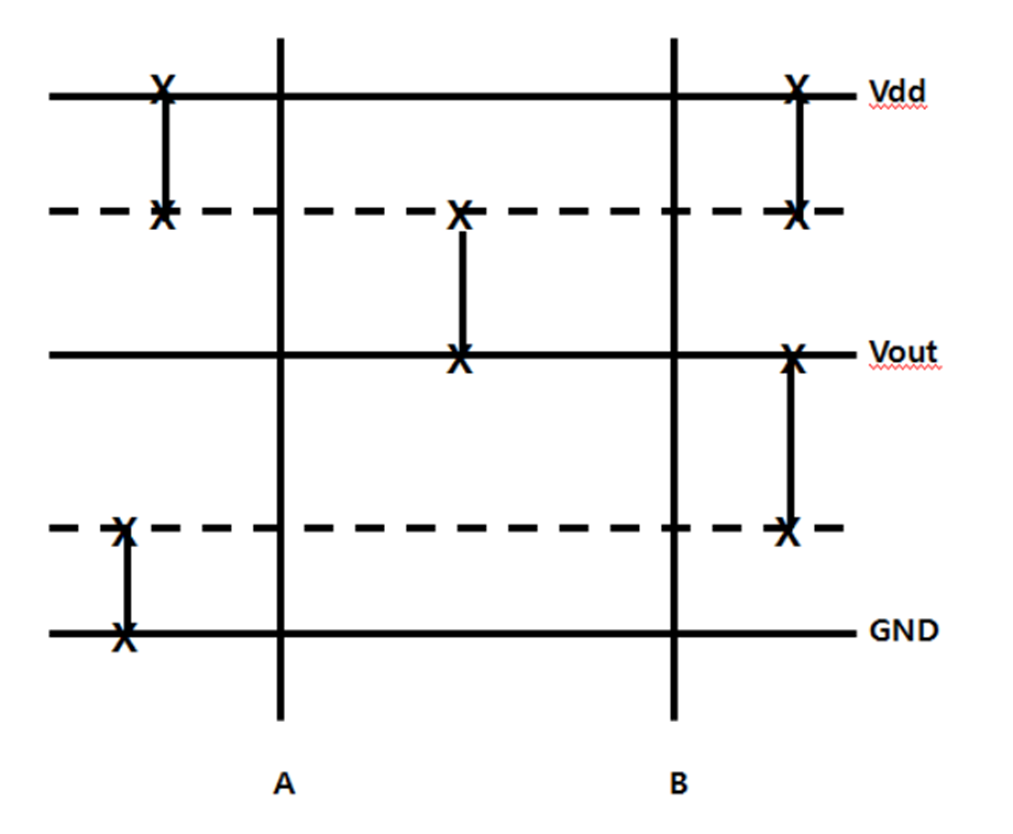

2NAND_STICK DIAGRAM

해당 내용들을 배우고 cadence virtuoso tool을 사용하는 법에 대해 배우게 되었다.

ONE CHIP LAYOUT을 제작하기 위해 사용한 TOOL은

CADENCE VIRTUOSO Schematic Editor / Layout Editor

SIMULATION - CADENCE VIRTUOSO SPECTRE / ADE

라이브러리 - GPDK090(90nn까지 공정 할 수 있는)

검증(LVS/DRC) - Assura 를 사용하였다.

'설계공부 > Full Custom IC One Chip Design' 카테고리의 다른 글

| FULL CHIP CUSTOM ONE CHIP DESIGN - 5(2X1 MUX LOGIC / SWITCH) (0) | 2023.08.07 |

|---|---|

| FULL CHIP CUSTOM ONE CHIP DESIGN - 5(3-4 NAND, NOR //LAYOUT) (0) | 2023.08.07 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 4(2NAND, 2NOR //LAYOUT) (0) | 2023.08.07 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 3(INVERTER, 2NAND, 2NOR, WIDTH) (0) | 2023.07.25 |

| FULL CHIP CUSTOM ONE CHIP DESIGN - 2(SCHEMATIC , STICK DIAGRAM) (0) | 2023.07.25 |