고정 헤더 영역

상세 컨텐츠

본문 제목

FULL CHIP CUSTOM ONE CHIP DESIGN - 11(4BIT_ADDER / 4BIT_ADDER_SUBTRACTOR)

본문

4BIT_ADDER

4BIT_ADDER는 4BIT인 2개의 입력신호를 더하는 역할을 하는 회로다.

진리표

4BIT_ADDER_구현방법

HALF_ADDER 1개와 FULL_ADDER3개로 구성하였으며, Tr의 갯수는 다음과 같다.

HALF_ADDER[(INVERTER3*2) + (2NAND4*4)] = 22개

+

FULL_ADDER[(INVERTER7*2) + (2NAND8*4) + (2NOR1*4) = 50개

총 72개

<4BIT_ADDER_SCHEMATIC>

<4BIT_ADDER_SIMBOL>

<4BIT_ADDER_TEST_SCHEMATIC>

<4BIT_ADDER_SIMULATION>

<4BIT_ADDER_LAYOUT>

세로 : 9.19 [um]

가로 : nMOS 37.54 [um]

AREA : 344.9926 [um2]

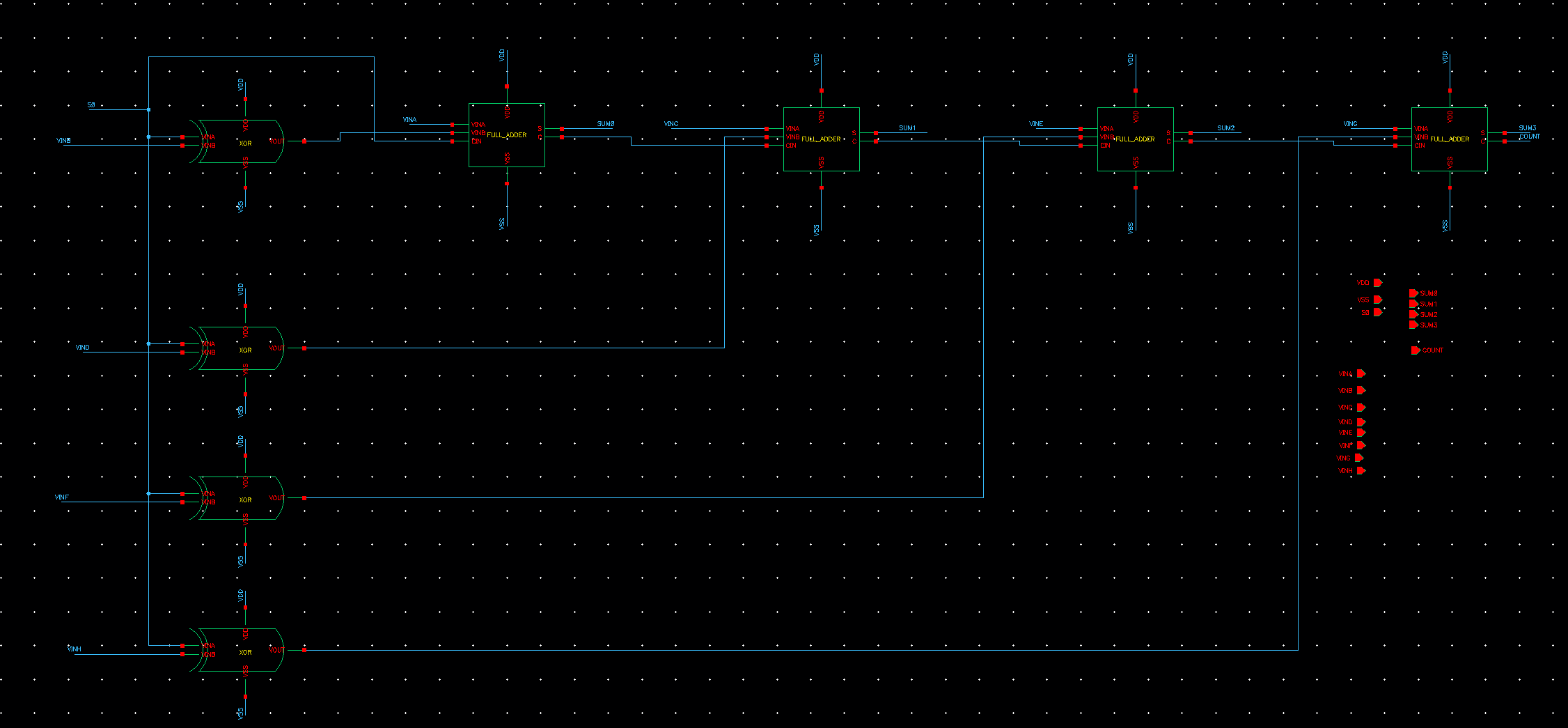

4BIT_ADDER_SUBTRACTOR

4BIT 가감산기의 뺄셈은 뺄셈이 아니고, INPUT 하나를 음수 형태로 바꾼 후 덧셈을 하는 방식으로,

2의 보수를 취함으로 음수로 바꾸기가 가능하다.

4BIT_ADDER_SUBTRACTOR_구현방법

XOR 4개와 FULL_ADDER 4개를 이용하여 4BIT_ADDER_SUBTRACTOR를 구성하였다.

Tr의 갯수는 다음과 같다.

XOR(6*4) = 24개

+

FULL_ADDER[(INVERTER7*2) + (2NAND8*4) + (2NOR1*4) = 50개

총 74개

<4BIT_ADDER_SUBTRACTOR_SCHEMATIC>

<4BIT_ADDER_SUBTRACTOR_SIMBOL>

<4BIT_ADDER_SUBTRACTOR_TEST_SCHEMATIC>

<4BIT_ADDER_SUBTRACTOR_SIMULATION>

<4BIT_ADDER_SUBTRACTOR_LAYOUT>

FULL_FIT_LAYOUT

세로 : 10.99 [um]

가로 : nMOS 61.08 [um]

AREA : 671.2692 [um2]