고정 헤더 영역

상세 컨텐츠

본문

0913

회로 잔상제거 : F5

시뮬레이션 잔상제거 : ctrl + L

출처 : https://www.futurlec.com/74/IC7432.shtml

쓰는 이유

7432 chip과 비교했을때

Diode Logic을 쓰면 필요부분만 사용가능하여 가격과 / 크기를 줄일 수 있다.

uni-derection

power line

bi-derection

signal line

High Z(하이 임피던스 회로)

해당 회로에서 입력단에서 Floating 되었을 때

PUL DOWN 저항은 BASE 저항보다 같거나 크게 만들어줘야하며, 제한적인 크기는 수백옴까지

PUL DOWN은 47k에서 정상동작 되지만,

더 높다면 소모전력을 줄일 수 있다 /

BUT 다 다른 저항을 쓰게 되면 생산시 단가가 올라 갈 수 있다.

[SPICE MODEL]

필요한 Data Sheet를 참조하여 SPICE MODEL을 가져와 .txt파일을 만들어주면 된다.

[Spice Model 추가방법]

DataSheet를 참조해 library를 다운 받고,

spice model 내용들을

txt파일에 옮겨준 후 OrCad 프로그램 내, Simulation Settings > Conflguration Files 에서

Category를 Library로 바꿔준 후 File 추가 , Add to Design 해주면 된다.

추가 이후 바꿔줄 Diode를 더블클릭하여

해당 값들의 이름을 SPICE MODEL명으로 변경해주면된다.

[LED 추가 - UPWLEDxx]

Base 저항을 더 크게 변경

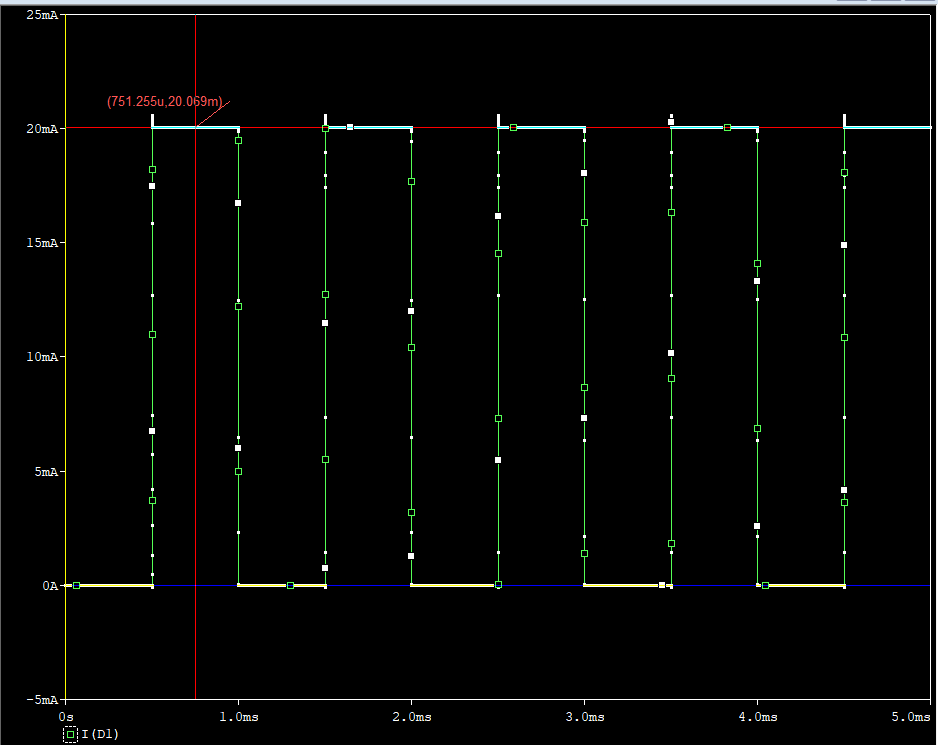

IF가 20mA로 흐르도록 했다.

따라서 표준저항인 47Ω으로 선택해서 측정했다.

전류가 흐르면 LED에는 전류 에너지가 열에너지로 변환되어 열이 발생한다.

따라서 전류가 잘흐르게 되면 열이 더 많이 발생하고 이 같은 과정이 계속 반복 된다. 이 현상을 열폭주라고 한다

그렇기 때문에 전류 제한이 필요하다.

Collector 저항을 1mΩ이 아닌 47Ω 그대로 사용해야 한다.

RC(Collector쪽 저항)를 47Ω 사용하고 RB(Base쪽 저항)를 더 줄여야 한다.

'설계공부 > 전자회로' 카테고리의 다른 글

| 전자회로 해석 및 설계-10(BJT 기반 inverter / Open collector = Open Drain) (0) | 2023.09.14 |

|---|---|

| 전자회로 해석 및 설계-9(SPEC에 따른 LED설계 및 해설) (0) | 2023.09.14 |

| 전자회로 해석 및 설계-7 (0) | 2023.09.12 |

| 전자회로 해석 및 설계-6 (0) | 2023.09.11 |

| 전자회로 해석 및 설계-5(공진과 댐핑저항) (0) | 2023.09.06 |