고정 헤더 영역

상세 컨텐츠

본문

제작기간 : 0921~0927

TOOL : OrCAD

Oscilloscope : Tektronix - TDS2012B

DC POWER SUPPLY : ED-333T

400ST160 DATA Sheet

자동차 후방 센서에 들어가는 Ultrasonic distance measurement Circuit가 있다.

Ultrasonic distance measurement Circuit 를 설계해 보았다.

설계의 목표

1. 1m거리가 측정되는 Ultrasonic distance measurement Circuit를 만드는것이다.

2. 측정거리는 [cm]단위이다.

3. FND의 출력은 FND1번에 1의자리, FND 2번에 10의자리, FND3번에 100의 자리가 나오게 하는것이다.

설계 SPEC

1. 초음파 주파수의 주파수는 40kHz

2. 초음파 주파수 펄스는 17Hz

설계의 순서

Algorithm Diagram > Schematic > Test / Debug

Ultrasonic distance measurement Circuit의 알고리즘이다.

크게 4부분으로 나누었다.

송신부 / 수신부 / 시간측정부분 / 출력부분

회로도는 두페이지로 나누었다.

#1

초음파 주파수 발진기, 초음파 펄스 주파수 발진기, 초음파 시간측정 회로, 초음파 수신회로, 검출 회로, 시그널 검출 회로

#2

시간측정기(SR LATCH), 카운터 클리어 펄스 레치 클리어 펄스 발진기, 카운터 펄스 발진기,

시간 측정회로, FND출력 회로

사용 부품

BOM

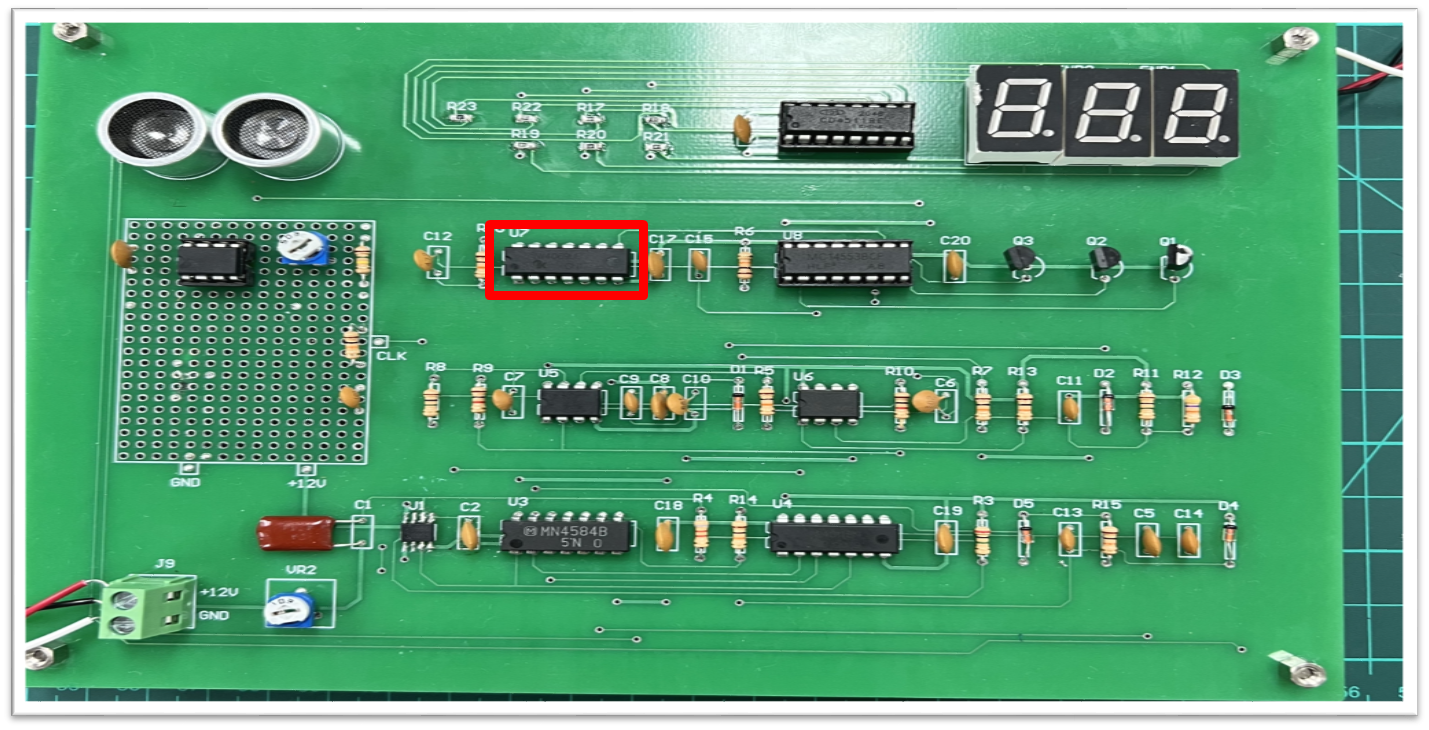

Bare board

Ultrasonic Oscillation

400ST160 DATA Sheet를 참고했다.

senter freq가 40kHz로 이거에 맞는 NE555 IC를 사용 했다.

주파수 발진부분에서는 항상 신호가 발진된다.

OrCad를 통해 회로도를 만들고 Simulation을 확인한 결과 40kHz가 제대로 나오는 것을 확인했다.

가변저항의 과부화로 인해 37kHz까지만 올려 Board 동작을 확인했다.

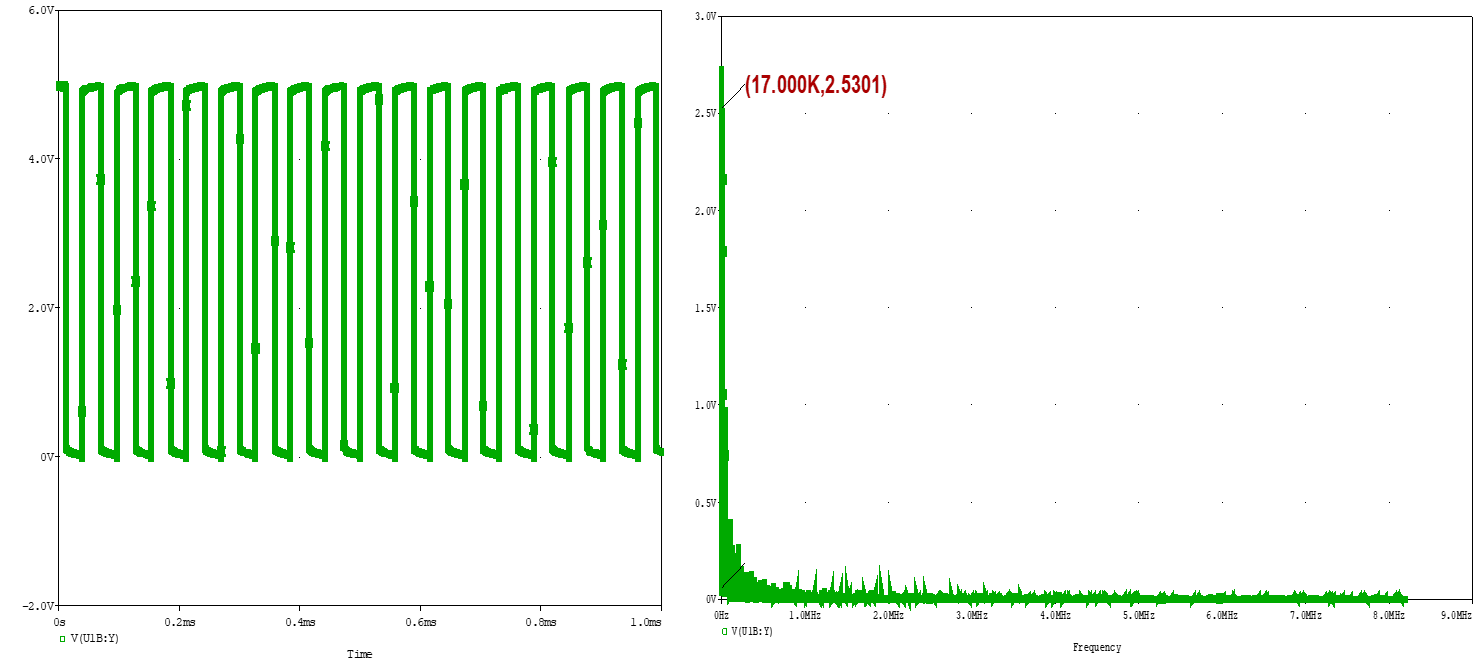

Ultrasonic Pulse Oscillator

주파수와 다르게 항상이 아닌 일정 시간에 발진하여

신호를 masking 해주는 역할을 한다.

simulation 결과 65.6ms로 나온다 따라서

주파수는 15Hz로 나온다.

f=1/T

=1/65.6

≃ 15Hz

Board 동작을 확인했다.

Oscilloscope 결과

Ultrasonic Transmission circuit

masking / 전력 전압 증폭이 일어나는 곳

앞단의 and 게이트에서 high신호가 masking 된다.

또한 U4,U3쪽 not gate를 사용한 이유는 hysteresis가 되기 때문에 전력의 증폭이 소폭 일어나 not gate를 사용

뒷단의 U5와 CAP을 이용하여, 위상 반전이 일으켜, 전압 증폭을 만들어 주었다.

이로 인해 신호검출에 필요한 신호를 크게 증폭시켰다.

simulation 결과

Oscilloscope 결과

Ultrasonic Receiving circuit

수신부에서도 증폭이 일어난다.

simulation 결과

100배 증폭이 제대로 일어나지 않는것을 확인할 수 있다.

왜그럴까?

고민해본 결과 앞단의 저항값이 너무크고 뒷단의 저항값이 너무 작아

증폭비가 제대로 안나오는것을 알 수 있다.

따라서 100k, 100k으로 나누어 증폭해야하는것을 확인했다.

Board test

Oscilloscope 결과

Detection circuit

신호 검출 회로

신호 검출을 위해 평활화가 진행된다.

평활화를 통해 필요없는 부분들을 걸려낸다.

Simulation 결과

평활화로인해 적색 그래프와 같이 깎인모습이다.

Board Test

Oscilloscope 결과

Signal Detection Circuit

Simulation결과

Board Test

Oscilloscope 결과

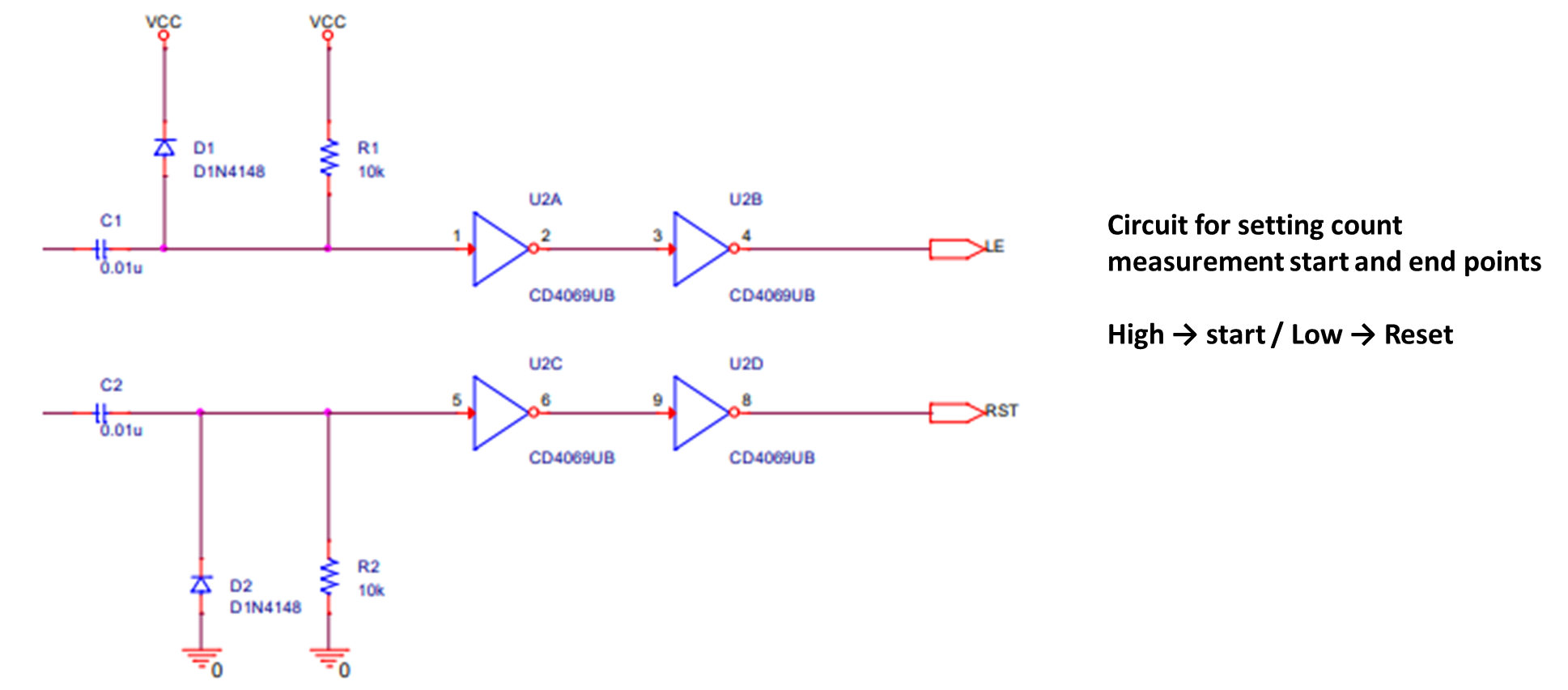

Transceiver Time Checker

Counter Pulse Generator

Counter Clear Pulse

Latch Clear Pulse Generator

FND Output Circuit

Soldering하는모습

Soldering

Operation Test

문제점

Soldering시 제대로 안되는 냉땜문제 >>> 일일이 다 찍어보며, 어느쪽이 문제인지 파악

Oscilloscope 측정시 voltage 확인 미흡, 이로인해급격한 DC power공급으로 인한 회로 과부화 >>> 항상 확인해야함,

캡장착

Noise문제 >>> GND / POWER 분리, POWER Beads or Cap 장착 (PI SI 증가 따라서 EMI감소)

증폭비 100배 안되는 문제 >>> 수신부 회로에서 R6, R7 10/10으로 나눠 증폭

BASE 저항과 BJT 없는 문제 >>> Base저항을 넣어 전류를 감소시켜 기생 커패시터의 충,방전 속도를 낮춰 Stablilty 증가

ESD 방지대첵 부족 >>> VCC 앞에 TVS 및 Varistor를 설치하여 ESD낮춤